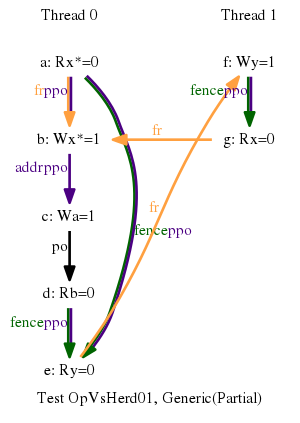

RISCV OpVsHerd01

(*

At some point was forbidden by rmem and allowed by herd

*)

{

0:s0=x; 0:s2=a; 0:s3=b; 0:s1=y;

1:s0=x; 1:s1=y;

}

P0 | P1 ;

li t1,1 | li t1,1 ;

lr.w a0,0(s0) | sw t1,0(s1) ;

sc.w a2,t1,0(s0) | fence rw,rw ;

xor a3,a2,a2 | lw a0,0(s0) ;

add s2,s2,a3 | ;

sw t1,0(s2) | ;

lw a4,0(s3) | ;

fence r,r | ;

lw a5,0(s1) | ;

Observed

1:x10=0; 0:x15=0; 0:x12=0;