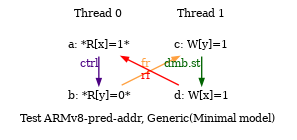

AArch64 ARMv8-pred-addr

(* In ARMv8, an address dependency where the dataflow pathway involves

only the control of a predicated instruction or conditional branch

doesn't count as an address dependency at all.

The following test should be allowed, because the CPU can speculate

the value of 1:r2 and then perform the read of y before the read of x.

*)

{

0:X7=x; 0:X8=y; 0:X9=u;

int *0:X2;

1:X7=x; 1:X8=y;

}

P0 | P1 ;

LDR W1,[X7] | MOV W0,#1 ;

CBNZ W1,Lelse | STR W0,[X8] ;

ADD X2,X9,#0 | DMB ST ;

B Lexit | MOV W2,#1 ;

Lelse: | STR W2,[X7] ;

ADD X2,X8,#0 | ;

Lexit: | ;

LDR W3,[X2] | ;

locations [0:X2;]

exists (0:X1=1 /\ 0:X3=0)