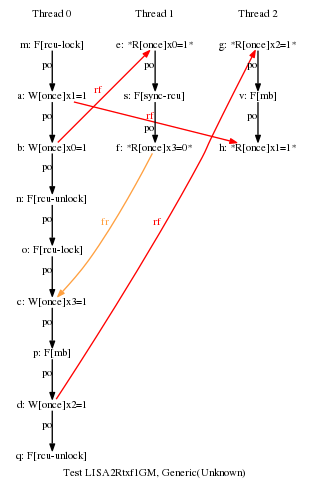

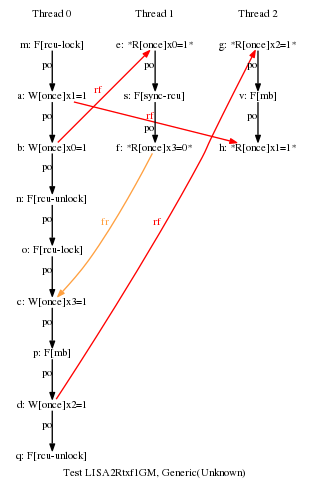

LISA LISA2Rtxf1GM

(*

* Result: Never

*

* Two RCU grace periods on a single thread and one RCU read-side critical

* section, but set up to verify that the pair of RCU read-side critical

* sections provide no ordering even when interacting with an intervening

* grace period, except for the memory barrier, which does enforce the needed

* ordering. Cycle forbidden.

*)

{

x0 = 0;

x1 = 0;

x2 = 0;

x3 = 0;

}

P0 | P1 | P2 ;

f[rcu_read_lock] | r[once] r0 x0 | r[once] r2 x2 ;

w[once] x1 1 | f[sync] | f[mb] ;

w[once] x0 1 | r[once] r3 x3 | r[once] r1 x1 ;

f[rcu_read_unlock] | | ;

f[rcu_read_lock] | | ;

w[once] x3 1 | | ;

f[mb] | | ;

w[once] x2 1 | | ;

f[rcu_read_unlock] | | ;

Observed

2:r2=1; 2:r1=1; 1:r3=0; 1:r0=1;