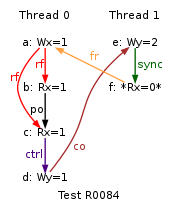

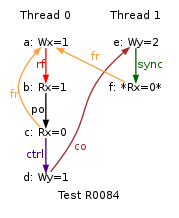

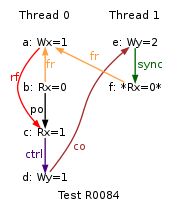

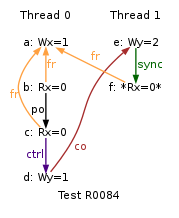

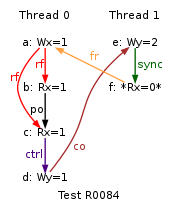

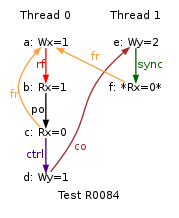

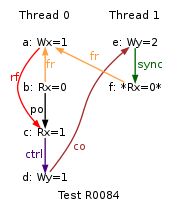

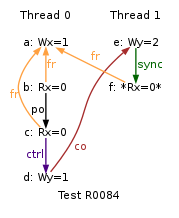

PPC R0084

"PosWR PosRR DpCtrldW Wse SyncdWR Fre"

Cycle=Fre PosWR PosRR DpCtrldW Wse SyncdWR

Relax=[Wse,SyncdWR,Fre]

Safe=PosWR PosRR DpCtrldW

Prefetch=0:x=F,0:y=W,1:y=F,1:x=T

Com=Ws Fr

Orig=PosWR PosRR DpCtrldW Wse SyncdWR Fre

{

0:r2=x; 0:r6=y;

1:r2=y; 1:r4=x;

}

P0 | P1 ;

li r1,1 | li r1,2 ;

stw r1,0(r2) | stw r1,0(r2) ;

lwz r3,0(r2) | sync ;

lwz r4,0(r2) | lwz r3,0(r4) ;

cmpw r4,r4 | ;

beq LC00 | ;

LC00: | ;

li r5,1 | ;

stw r5,0(r6) | ;

exists

(y=2 /\ 1:r3=0)