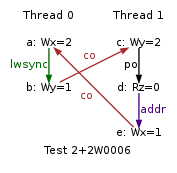

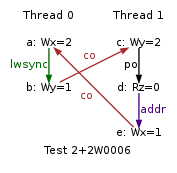

PPC 2+2W0006

"LwSyncdWW Wse PodWR DpAddrdW Wse"

Cycle=Wse PodWR DpAddrdW Wse LwSyncdWW

Relax=[Wse,LwSyncdWW,Wse]

Safe=PodWR DpAddrdW

Prefetch=0:x=F,0:y=W,1:y=F,1:x=W

Com=Ws Ws

Orig=LwSyncdWW Wse PodWR DpAddrdW Wse

{

0:r2=x; 0:r4=y;

1:r2=y; 1:r4=z; 1:r7=x;

}

P0 | P1 ;

li r1,2 | li r1,2 ;

stw r1,0(r2) | stw r1,0(r2) ;

lwsync | lwz r3,0(r4) ;

li r3,1 | xor r5,r3,r3 ;

stw r3,0(r4) | li r6,1 ;

| stwx r6,r5,r7 ;

exists

(x=2 /\ y=2)