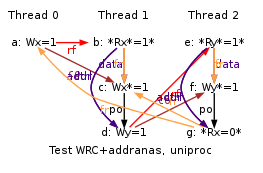

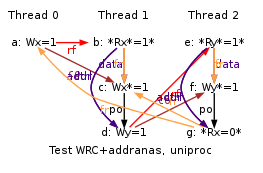

ARM WRC+addranas

"RfeNaA DpAddrdWANa RfeNaA DpAddrdRANa Fre"

Cycle=RfeNaA DpAddrdWANa RfeNaA DpAddrdRANa Fre

Prefetch=1:x=F,1:y=W,2:y=F,2:x=T

Com=Rf Rf Fr

Orig=RfeNaA DpAddrdWANa RfeNaA DpAddrdRANa Fre

{ ok=1;

%x0=x;

%x1=x; %y1=y; %ok1=ok;

%y2=y; %x2=x; %ok2=ok;

}

P0 | P1 | P2 ;

MOV R0,#1 | LDREX R0,[%x1] | LDREX R0,[%y2] ;

STR R0,[%x0] | STREX %T2,R0,[%x1] | STREX %T2,R0,[%y2] ;

| CMP %T2,#0 | CMP %T2,#0 ;

| BNE Fail1 | BNE Fail2 ;

| EOR R1,R0,R0 | EOR R1,R0,R0 ;

| MOV R2,#1 | LDR R2,[R1,%x2] ;

| STR R2,[R1,%y1] | B Exit2 ;

| B Exit1 | Fail2: ;

| Fail1: | MOV R3,#0 ;

| MOV R3,#0 | STR R3,[%ok2] ;

| STR R3,[%ok1] | Exit2: ;

| Exit1: | ;

Observed

1:R0=1; 2:R0=1; 2:R2=0; ok=1; x=1; y=1;