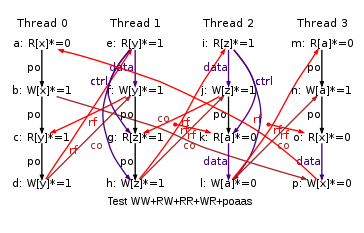

PPC WW+RW+RR+WR+poaas

"PodWWAA RfeAA PodRWAA RfeAA PodRRAA FreAA PodWRAA FreAA"

Prefetch=2:a=T,3:x=T

Com=Rf Rf Fr Fr

Orig=PodWWAA RfeAA PodRWAA RfeAA PodRRAA FreAA PodWRAA FreAA

{ ok=1;

0:r2=x; 0:r4=y; 0:r6=ok;

1:r2=y; 1:r4=z; 1:r6=ok;

2:r2=z; 2:r4=a; 2:r6=ok;

3:r2=a; 3:r4=x; 3:r6=ok;

}

P0 | P1 | P2 | P3 ;

li r1,1 | lwarx r1,r0,r2 | lwarx r1,r0,r2 | li r1,1 ;

lwarx %sta,r0,r2 | stwcx. r1,r0,r2 | stwcx. r1,r0,r2 | lwarx %sta,r0,r2 ;

stwcx. r1,r0,r2 | bne Fail1 | bne Fail2 | stwcx. r1,r0,r2 ;

bne Fail0 | li r3,1 | lwarx r3,r0,r4 | bne Fail3 ;

li r3,1 | lwarx %sta,r0,r4 | stwcx. r3,r0,r4 | lwarx r3,r0,r4 ;

lwarx %sta,r0,r4 | stwcx. r3,r0,r4 | bne Fail2 | stwcx. r3,r0,r4 ;

stwcx. r3,r0,r4 | bne Fail1 | b Exit2 | bne Fail3 ;

bne Fail0 | b Exit1 | Fail2: | b Exit3 ;

b Exit0 | Fail1: | li r5,0 | Fail3: ;

Fail0: | li r5,0 | stw r5,0(r6) | li r5,0 ;

li r5,0 | stw r5,0(r6) | Exit2: | stw r5,0(r6) ;

stw r5,0(r6) | Exit1: | | Exit3: ;

Exit0: | | | ;

~exists

(ok=1 /\ 1:r1=1 /\ 2:r1=1 /\ 2:r3=0 /\ 3:r3=0)