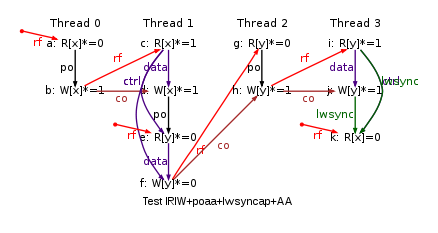

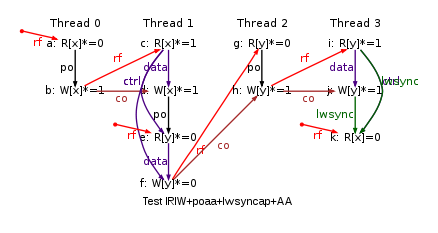

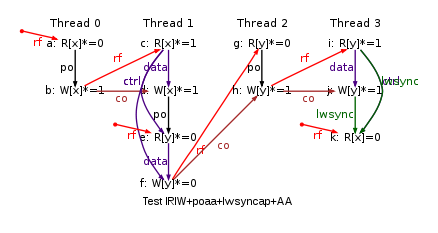

PPC IRIW+poaa+lwsyncap+AA

"RfeAA PodRRAA FreAA RfeAA LwSyncdRRAP FrePA"

Cycle=RfeAA PodRRAA FreAA RfeAA LwSyncdRRAP FrePA

Prefetch=0:x=T,1:y=T,2:y=T,3:x=T

Com=Rf Fr Rf Fr

Orig=RfeAA PodRRAA FreAA RfeAA LwSyncdRRAP FrePA

{ ok=1;

0:r2=x; 0:r4=ok;

1:r2=x; 1:r4=y; 1:r6=ok;

2:r2=y; 2:r4=ok;

3:r2=y; 3:r4=x; 3:r6=ok;

}

P0 | P1 | P2 | P3 ;

li r1,1 | lwarx r1,r0,r2 | li r1,1 | lwarx r1,r0,r2 ;

lwarx %sta,r0,r2 | stwcx. r1,r0,r2 | lwarx %sta,r0,r2 | stwcx. r1,r0,r2 ;

stwcx. r1,r0,r2 | bne Fail1 | stwcx. r1,r0,r2 | bne Fail3 ;

bne Fail0 | lwarx r3,r0,r4 | bne Fail2 | lwsync ;

b Exit0 | stwcx. r3,r0,r4 | b Exit2 | lwz r3,0(r4) ;

Fail0: | bne Fail1 | Fail2: | b Exit3 ;

li r3,0 | b Exit1 | li r3,0 | Fail3: ;

stw r3,0(r4) | Fail1: | stw r3,0(r4) | li r5,0 ;

Exit0: | li r5,0 | Exit2: | stw r5,0(r6) ;

| stw r5,0(r6) | | Exit3: ;

| Exit1: | | ;

exists

(ok=1 /\ 1:r1=1 /\ 1:r3=0 /\ 3:r1=1 /\ 3:r3=0)