### Moscova

Jean-Jacques Lévy

INRIA Paris-Rocquencourt

March 23, 2011

▲□▶ ▲□▶ ▲ 三▶ ★ 三▶ 三三 - のへぐ

## **Research team**

・ロト ・ 日 ・ モ ト ・ モ ・ うへで

#### • Staff 2008-2011

Jean-Jacques Lévy, INRIA Karthikevan Bhargavan, INRIA James Leifer, INRIA Luc Maranget, INRIA Francesco Zappa Nardelli, INRIA Ricardo Corin, INRIA → Cordoba Gilles Peskine, INRIA ---> Trusted logic Pierre-Malo Deniélou, INRIA → Imperial College Jade Alglave, INRIA — Oxford Jérémy Planul, MSR-INRIA

- Moscova history:

- ▶ Para (1988, Head: Lévy), Moscova (2000, Head: Gonthier → MSRC)

- 18 PhDs

- 75% Cog proof of the 4-color thm; debugging of 3 modules of Ariane-501 PV; spinoff of Polyspace [Alain Deutsch]; etc.

- ▶ Polytechnique (Lévy, prof 1992-2006) → MSR-INRIA Joint Centre (Head: Lévy)

# **Research themes**

・ロト ・ 日 ・ モ ト ・ モ ・ うへで

• programming languages

safe marshalling, ott, like types

• concurrency

[jocaml, separation logic/c-minor/concurrency, weak memory models]

security compilers and verifiers [secure sessions, audits, tls, information flow]

## **Research results**

・ロト ・ 日 ・ モ ト ・ モ ・ うへで

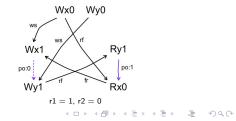

- memory models of multi-core processors

- give formal description of WMMs

- operational semantics of WMMs

- certified (back-end) compiler for some WMMs

- prove correctness of compiler optimisations in WMMs

## 2.1 Loads are not reordered with other loads and stores are not reordered with other stores

Intel 64 memory ordering ensures that loads are seen in program order, and that stores are seen in program order.

| Processor 0                                                   | Processor 1                             |  |

|---------------------------------------------------------------|-----------------------------------------|--|

| mov [ _x], 1 // M1<br>mov [ _y], 1 // M2                      | mov r1,[_y] // M3<br>mov r2, [_x] // M4 |  |

| Initially $x == y == 0$<br>r1 == 1 and r2 == 0 is not allowed |                                         |  |

Table 2.1: Stores are not reordered with other stores

#### 2.3 Loads may be reordered with older stores to different locations

Intel 64 memory ordering allows load instructions to be reordered with prior stores to a different location. However, loads are not reordered with prior stores to the same location.

The first example in this section illustrates the case in which a load may be reordered with an older store – i.e. if the store and load are to different non-overlapping locations.

| Processor 0                    | Processor 1        |  |

|--------------------------------|--------------------|--|

| mov [ _x], 1 // M1             | mov [ _y], 1 // M3 |  |

| mov r1, [_y] // M2             | mov r2, [_x] // M4 |  |

| Initially x == y == 0          |                    |  |

| r1 == 0 and r2 == 0 is allowed |                    |  |

Table 2.3.a: Loads may be reordered with older stores

#### 2.5 Stores are transitively visible

Intel 64 memory ordering ensures transitive visibility of stores – i.e. stores that are causally related appear to execute in an order consistent with the causal relation.

| Processor 0                                                         | Processor 1                             | Processor 2                                |

|---------------------------------------------------------------------|-----------------------------------------|--------------------------------------------|

| mov [ _x], 1 // M1                                                  | mov r1, [_x] // M2<br>mov [_y], 1 // M3 | mov r2, [ _y] // M4<br>mov r3, [ _x] // M5 |

| Initially $x == y == 0$<br>r1 == 1, r2 == 1, r3 == 0 is not allowed |                                         |                                            |

Table 2.5: Stores are transitively visible

• In SC, program order is strictly respected.

◆□ > ◆□ > ◆豆 > ◆豆 > ・豆 = のへで

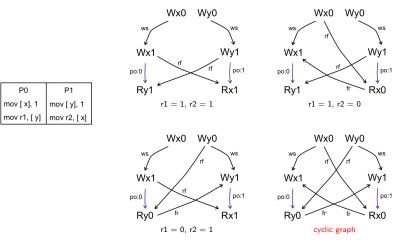

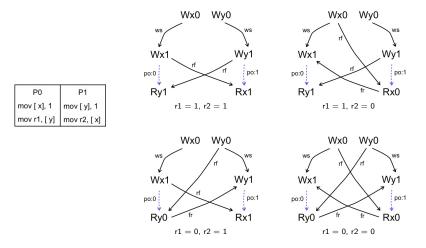

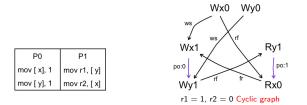

• In TSO, W followed by R can be relaxed within program order

• In TSO, W followed by R relaxed

• In PSO, W followed by W to distinct location relaxed

| P0          | P1           |

|-------------|--------------|

| mov [ x], 1 | mov r1, [ y] |

| mov [ y], 1 | mov r2, [ x] |

#### Weak memory models

- axiomatic + operational models for Intel [~Cambridge] / Power [~INRIA]

- formalisation in HOL/Coq

- tests on real processor behaviour http://www.cl.cam.ac.uk/~pes20/ppc-supplemental/ppc003.html

- formal proof of simple concurrent code (eg. Linux spinlocks)

- operational reasoning: data-race freedom, separation logic

- certified compiler for concurrent languages http://www.cl.cam.ac.uk/~pes20/CompCertTS0

[Zappa Nardelli, Maranget, Alglave, Braibant, Sewell et al]

[POPL 09, CACM 10; DAMP 09, CAV 10, PLDI 11; TACAS 11; POPL 11]

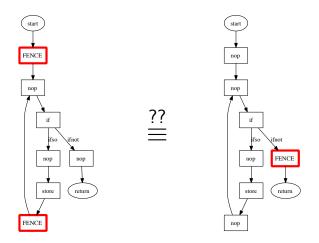

#### Weak memory models

• Proving correctness of optimisations

Fences elimination with TSO  $\simeq$  3 kloCoq

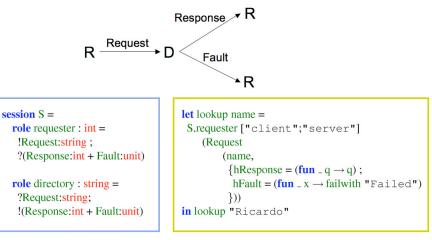

#### EXAMPLE 2 Secure sessions

- passing authenticated (signed) values between 2 run-times

- design of a mini F# + primitives for authentication

+ global contract with sessions types

- compiling scheme into a low-level language ( $\simeq$  pi-calculus) to describe authentication protocols

- formal proof of its correctness, with security property induced by strong typing of F# + usage of authentication primitives

- extension to other security properties, sessions V2 (privacy of message values, integrity, dynamic number of principals, etc)

[Corin, Deniélou, Leifer, Fournet, Bhargavan]

#### EXAMPLE 2 Secure sessions

- passing authenticated (signed) values between 2 run-times

- design of a mini F# + primitives for authentication

+ global contract with sessions types

- compiling scheme into a low-level language ( $\simeq$  pi-calculus) to describe authentication protocols

- formal proof of its correctness, with security property induced by strong typing of F# + usage of authentication primitives

- extension to other security properties, sessions V2 (privacy of message values, integrity, dynamic number of principals, etc)

#### EXAMPLE 2 Secure sessions

- passing authenticated (signed) values between 2 run-times

- design of a mini F# + primitives for authentication + global contract with sessions types

- compiling scheme into a low-level language (≃ pi-calculus) to describe authentication protocols

- formal proof of its correctness, with security property induced by strong typing of F# + usage of authentication primitives

- extension to other security properties, sessions V2 (privacy of message values, integrity, dynamic number of principals, etc)

[Corin, Deniélou, Leifer, Fournet, Bhargavan]

### Simple exchange

Session declaration

#### User code

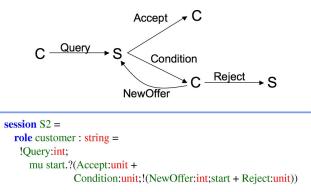

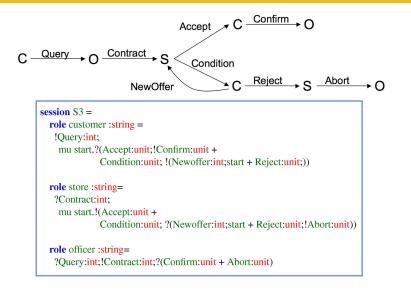

#### Two-party negotiation

▲ロト ▲帰 ト ▲ ヨ ト ▲ ヨ ト ● ● ● ● ● ●

#### Three-party session

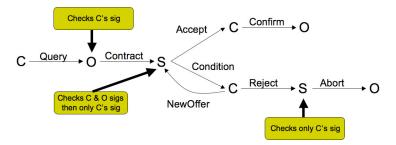

## Visibility

- Minimal sequence of signatures that guarantee session compliance.

- Example:

▲ロト ▲帰 ト ▲ ヨ ト ▲ ヨ ト ● ● ● ● ● ●

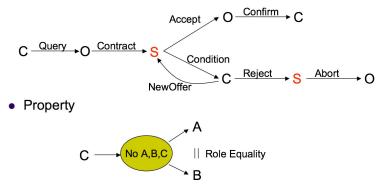

### No blind fork

• Some forks in protocols represent a security threat.

#### Secure sessions

- passing authenticated (signed) values between 2 run-times

- design of a mini F# + primitives for authentication + global contract with sessions types

- compiling scheme into a low-level language ( $\simeq$  pi-calculus) to describe authentication protocols

- formal proof of its correctness, with security property induced by strong typing of F# + usage of authentication primitives

- extension to other security properties, sessions V2 (privacy of message values, integrity, dynamic number of principals, etc)

[Corin, Deniélou, Leifer, Fournet, Bhargavan]

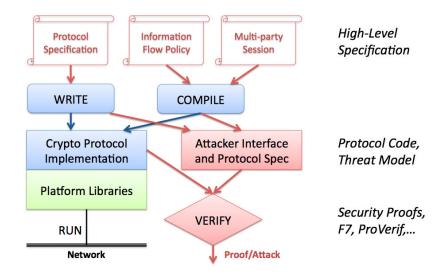

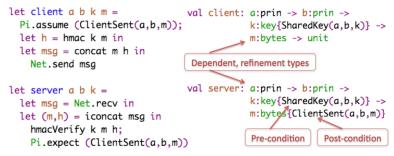

#### EXAMPLE 3 Verified Crypto Protocol Implementations

・ロト ・ 日下 ・ 日下 ・ 日下 ・ 今々で

### Protocol Specifications in F7

#### $A \rightarrow B: m, hmac k_{AB} m$

#### F# Code

#### F7 Interface

▲ロト ▲帰 ト ▲ ヨ ト ▲ ヨ ト ● ● ● ● ● ●

### Protocol Specifications in F7

#### $A \rightarrow B$ : m, hmac k<sub>AB</sub> m

#### F# Code

#### **Refined Crypto Interface**

```

let client a b k m =

val hmac: k:key{MKey(k)} ->

Pi.assume (ClientSent(a,b,m));

m:bytes{MayMAC(k,m)} ->

let h = hmac k m in

h:bytes

Pre-conditions

let msg = concat m h in

Net.send msa

val hmacVerify: k:kev{MKev(k)} ->

m:bytes -> h:bytes ->

let server a b k =

unit{MayMAC(k,m)}

let msg = Net.recv in

Post-condition

let (m,h) = iconcat msg in

hmacVerify k m h;

assume !a.b.k.

SharedKey(a,b,k) \Rightarrow MKey(k)

Pi.expect (ClientSent(a,b,m))

assume !a.b.k.

SharedKey(a,b,k) \Rightarrow

```

(!m. MayMAC(k,m) <=> ClientSent(a,b,m))

▲ロト ▲帰 ト ▲ ヨ ト ▲ ヨ ト ● ● ● ● ● ●

## TLS in F#

#### We implemented a subset of TLS (10 kLOC)

- Supports SSL3.0, TLS1.0, TLS1.1 DES, AES, RC4, SHA1, MD5

- Largest verified crypto protocol implementation till date

- We used "global" cryptographic verifiers, ProVerif and CryptoVerif [Blanchet]

We reached the limit of this proof method:

- Whole-program analysis does not scale

- Verification takes hours on a large machine

Ongoing work: Use F7 for modular verification

[CCS 08, TOPLAS 10, APLAS 10, POPL 10, ESORICS 09, phD Guts'11]

▲ロト ▲冊 ト ▲ ヨ ト → ヨ ト → の へ つ

- Acute type safed marshalling [Leifer, Peskine, Zappa Nardelli]

- OTT A semantics tool [Sewell, Zappa Nardelli]

- Scripting languages (Like types) [Zappa Nardelli]

- Jocaml (version 3; more portable, documentation) [Maranget, Mandel]

- Separation logic [Appel, Zappa Nardelli]

- Security through logs [Guts, Fournet, Zappa Nardelli]

- Information flow [Corin, Fournet, le Guernic, Planul, Rezk]

- Pattern-matching in Ocaml [Maranget]

# **Miscellaneous**

・ロト ・ 日 ・ モ ト ・ モ ・ うへで

• Microsoft Research Cambridge through the MSR-INRIA Joint Centre

- Sewell et al at Cambridge, Computer Lab

- Indes, Celtique, PPS with ANR Parsec [Zappa Nardelli]

- Gallium for general discussion about programming languages

- Andrew Appel, Princeton

- Secsi, Cascade with ERC-Crysp [Bhargavan]

### Software

- diy tool suite [Alglave, Maranget]

- OTT: a semantics tool [Sewell, Zappa Nardelli]

- CompCertTSO: certified compiler for TSO [Jagannathan, Sewell, Sevcik, Vafeiadis, Zappa Nardelli]

- S2ML [Bhargavan, Corin, Deniélou]

- FS2CV [Bhargavan, Corin, Zalinescu]

- F7 [Bhargavan]

- Jocaml [Maranget, Mandel]

- 5% Ocaml (pattern matching) [Maranget]

- Hévéa: an efficient translator of Tex into Html [Maranget]

- MPRI (master course at Paris 7) [Zappa Nardelli, Leifer]

- École polytechnique [Maranget, Bhargavan, ...Lévy (1992-2006)] lecture notes + web pages

- Entrance examination at Polytechnique [Maranget (4 years), Lévy (??-2009)]

• Bertinoro, IIT-Delhi, Tsinghua, etc.

# **Objectives for next years**

・ロト ・ 日 ・ モ ト ・ モ ・ うへで

## Scientific goals

- Weak Memory Models

- ► **ARM** multi-core + xfer to industry

- automatic exploration of WMMs

- automatic synchronisation of programs

- certified compilation of C-like with C1x/C++0x WMM

- Security compilers and verifiers

- scalable tools to verify security of programs

- verified open source cryptographic libraries

- web applications with formal proofs of security

## Organization

INRIA

### Organization

INRIA

イロト イロト イモト イモト 三日

# FIN

12 April 2011: http://msr-inria.inria.fr/forum2011